【視頻】基于Web服務(wù)器的可重構(gòu)硬件測控平臺(tái)(第一屆OpenHW開源硬件與嵌入式大賽二等獎(jiǎng))

發(fā)表于:6/15/2012

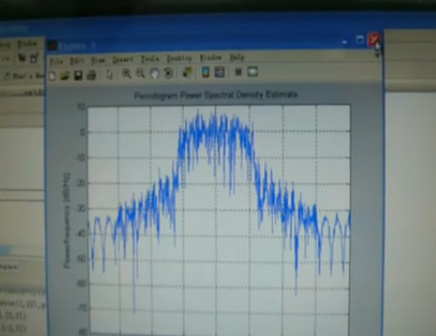

【視頻】WCDMA系統(tǒng)數(shù)字頻域干擾抵消器2(第一屆OpenHW開源硬件與嵌入式大賽一等獎(jiǎng))

發(fā)表于:6/15/2012

【視頻】WCDMA系統(tǒng)數(shù)字頻域干擾抵消器1(第一屆OpenHW開源硬件與嵌入式大賽一等獎(jiǎng))

發(fā)表于:6/15/2012

【視頻】基于網(wǎng)絡(luò)編碼的多信源組播通信系統(tǒng)(第二屆OpenHW開源硬件與嵌入式大賽一等獎(jiǎng))

發(fā)表于:6/15/2012

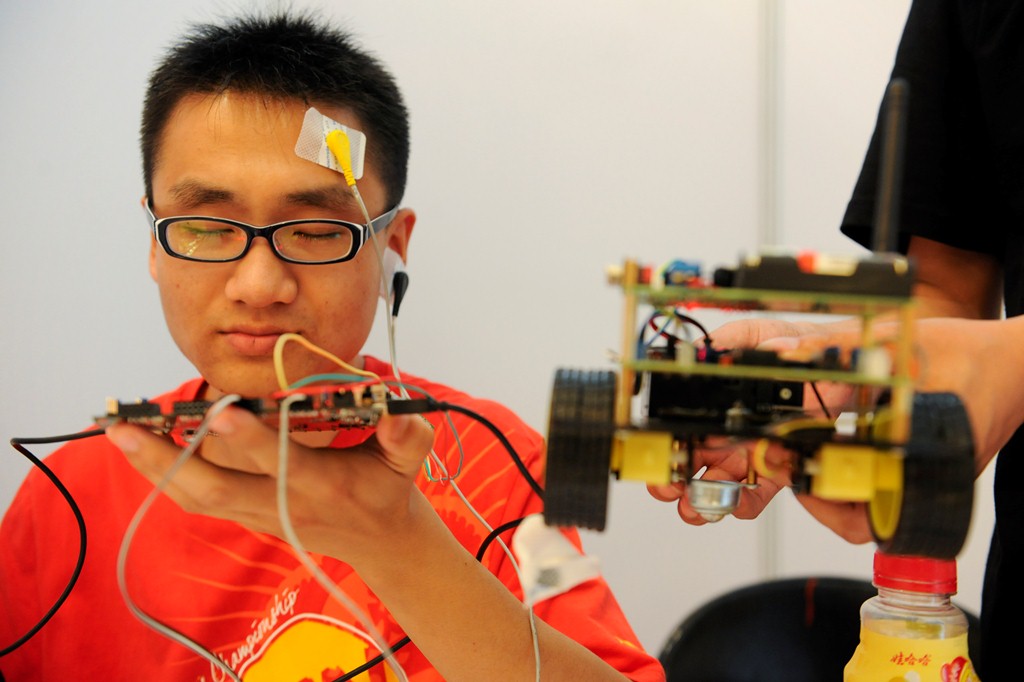

【視頻】基于FPGA的情緒檢測程序與相關(guān)智能寵物的開發(fā)(第三屆OpenHW開源硬件與嵌入式大賽二等獎(jiǎng))

發(fā)表于:6/14/2012

【視頻】基于FPGA的嵌入式智能監(jiān)控小車(第三屆OpenHW開源硬件與嵌入式大賽優(yōu)勝獎(jiǎng))

發(fā)表于:6/14/2012

【視頻】AVS編碼FPGA實(shí)現(xiàn)(第三屆OpenHW開源硬件與嵌入式大賽二等獎(jiǎng))

發(fā)表于:6/14/2012